### Rapidly Maturing SiC Junction Transistors Featuring Current Gain ( $\beta$ ) > 130, Blocking Voltages Up To 2700 V and Stable Long-Term Operation

S.G. Sundaresan, S. Jeliazkov, B. Grummel, R. Singh

GeneSiC Semiconductor, Inc. 43670 Trade Center PI, Suite 155, Dulles, VA 20166, USA

Email: siddarth.sundaresan@genesicsemi.com (corresponding author)

Keywords: SiC BJT, Current Gain, Breakdown Voltage, On-Resistance, Ultrafast Switching

**Abstract.** SiC *npn* Junction Transistors (SJTs) with current gains as high as 132, low on-resistance of 4 m $\Omega$ -cm<sup>2</sup>, and minimal emitter-size effect are demonstrated with blocking voltages > 600 V. 2400 V-class SJTs feature blocking voltages as high as 2700 V combined with on-resistance as low as 5.5 m $\Omega$ -cm<sup>2</sup>. A significant improvement in the current gain stability under long-term high current stress is achieved for the SJTs fabricated by the high gain process.

### Introduction

The static, switching and reliability characteristics of first-generation (Gen-I) 1200 V SiC SJTs were reported in [1], while 10 kV SJT results were presented in [2]. The Gen-I SiC SJTs featured a current gain ( $\beta$ ) in the range of 70-80, robust avalanche mode operation, and < 25 ns switching capability. Subsequent refinements to the SJT design/process suite have resulted in large-area (chip size = 1.9-6.3 mm<sup>2</sup>) Gen-II transistors with  $\beta$  >130. The electrical characteristics of these high-gain, Gen-II SiC SJTs, 2400 V-class SiC SJTs, optimized gate drive techniques and device stability results from long-term, high-current operation are presented in this paper. The SJTs featured in this article were packaged in either plastic TO-247 or metal TO-257 headers for high temperature/switching investigations.

### High-Current Gain (Gen-II) SiC SJTs

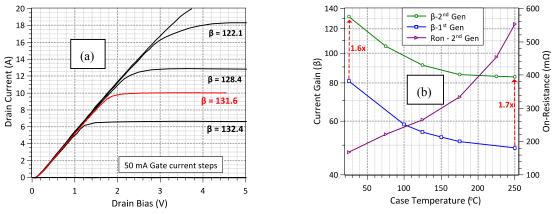

Purely majority-carrier like output characteristics with near- $\infty$  Early voltage are observed in the room-temperature output characteristics (see Fig. 1a) of a 3.5 mm<sup>2</sup> Gen-II SiC SJT, packaged in a high-temperature TO-257 header. The  $\beta$  in the active region is as high as 132 for drain current in the range of 6.5 A – 10 A, which corresponds to current densities of 260-400 A/cm<sup>2</sup>, respectively. The current gain shows an expected negative temperature co-efficient (Fig. 1b) due to the increasing ionization of Al acceptors in the base layer. However, a  $\beta$  as high as 84 is observed at 250°C, which is 1.7 x higher than the current gain measured on Gen-I SJTs.

Figure 1 (a): Output characteristics of a 3.5 mm<sup>2</sup> SiC SJT (active area = 2.5 mm<sup>2</sup>) fabricated by the high-gain process and (b): Temperature variation of  $\beta$  and Ron for 3.5 mm<sup>2</sup> Gen-I and Gen-II SiC SJTs.

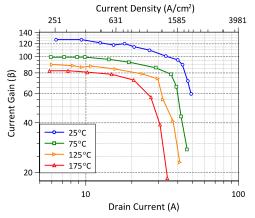

While current gains as high as 257 were reported [3] on single-finger test BJTs, the devices reported in this paper show the highest current gain ever recorded on a multi-ampere power transistor, which also display robust blocking voltages > 600 V. The variation of  $\beta$  at extremely high drain current densities (up to 2000 A/cm<sup>2</sup>) was investigated by single 3 µs-wide, 10 Hz pulsed current measurements on 3.5 mm<sup>2</sup> Gen-II SJTs (Fig. 2) to minimize any device self-heating. The current gain is relatively flat up to 800 A/cm<sup>2</sup> at all temperatures, indicating a low surface recombination velocity. The knee-current above which the  $\beta$  rolls off steeply reduces from 1700 A/cm<sup>2</sup> at 25°C to about 800 A/cm<sup>2</sup> at 175°C, from which the safe-operating area for high pulsed current SJT operation can be inferred. The electron mobility decreases with increasing temperature, which in turn increases the voltage drop across the low doped n- drift layer for a fixed drain current. This increased voltage drop causes the p-base/n- layer to become forward biased at a lower drain current at high temperatures, thereby lowering the knee current for  $\beta$  roll-off.

Figure 2: Current gain of a packaged 3.5 mm<sup>2</sup> SiC SJT at ultra-high current densities investigated by pulsed current measurements at various temperatures. Note that these knee currents are significantly lower than the threshold current for the onset of the Kirk effect, which is calculated as 14.3 kA/cm<sup>2</sup> using the SiC material and SJT epitaxial parameters

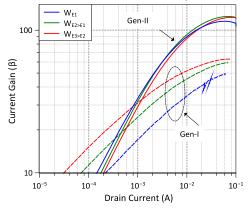

The  $\beta$  vs I<sub>D</sub> relationship in the sub-threshold regime (Fig. 3) was investigated by Gummel-plot measurements for several test SJTs fabricated with different Source finger widths in the range of 10-40 µm, by the Gen-I and Gen-II processes. In addition to the higher  $\beta$  values, the Gen-II process results in a drastic reduction of the emitter-size effect, which implies a significant reduction of the surface recombination velocity for the devices fabricated by the Gen-II process.

Figure 3: Emitter-size effect for SiC SJTs investigated by Gummel-plot measurements in the sub-threshold regime ( $V_{DS} = 5$  V). The Gen-II SJTs demonstrate a significantly reduced emitter-size effect in addition to achieving higher values of current gain over their Gen-I counterparts.

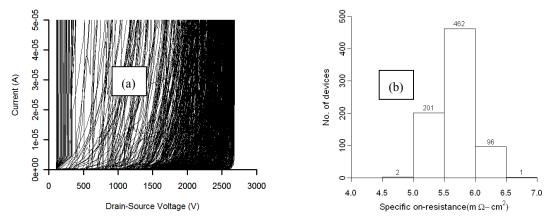

The 2400 V-class SiC SJTs were fabricated on 15  $\mu$ m thick/8 x 10<sup>15</sup> cm<sup>-3</sup> doped SiC epilayers. These devices were fabricated using the "Gen-I" process, yielding current gains ( $\beta$ ) in the range of 60-70. Open-base breakdown I-V characteristics from over 700, 3.5 mm<sup>2</sup> SiC SJTs fabricated on one SiC wafer are shown in Fig. 4a. A tight grouping of devices with sharp avalanche breakdown characteristics is observed in the range of 2200 – 2700 V, which corresponds to almost 100% of the avalanche rating, calculated by integrating the 4H-SiC impact ionization co-efficients. On-resistance histograms from 650, packaged 3.5 mm<sup>2</sup> SiC SJTs with a minimum blocking voltage of 2200 V (see Fig. 4b) show values in the range of 5 – 6.5 mΩ-cm<sup>2</sup>. A unipolar figure of merit  $(V_B^2/R_{ON,SP})$  in the range of of 0.8 - 1.3 GW/cm<sup>2</sup> is calculated from these results, which is among the highest ever reported on a majority carrier power device (or a device without conductivity modulation of the drift layer).

# Figure 4 (a): Open-base breakdown characteristics measured on all 3.5 mm<sup>2</sup> SiC SJTs fabricated on one 100 mm SiC wafer and (b): Histogram of specific on-resistance extracted from pulsed I-V measurements on about 650 TO-247 packaged SJTs, also displaying a minimum blocking voltage of 2200 V.

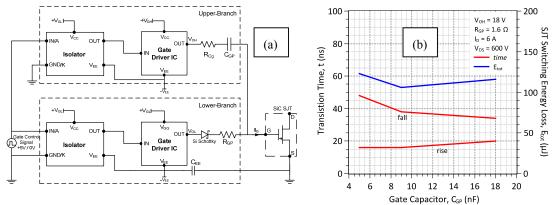

A two voltage level driver schematic initially proposed in [4] (see Fig. 5a) features a lower voltage branch (V<sub>OL</sub>) connected in series with an external gate resistor to maintain low steady-state driver losses, while the other gate drive IC in series with an external gate capacitor (C<sub>GP</sub>) supplies a higher output voltage (V<sub>OH</sub>) for achieving high dynamic gate currents. Since the Gate-Source junction of the SJT turns-on at  $\approx 3$  V, it can be effectively driven by gate voltages as low as 4-5 V, in stark contrast to SiC MOSFETs, which require drive voltages as high as 20 V. The values of the gate resistor and capacitor need to be optimized for minimizing the driver loss as well as the SJT switching losses. For example, at  $C_{GP} = 9$  nF, the SJT drain current switching times,  $t_r$ ,  $t_f$  and device switching energy losses,  $E_{tot}$  for a 1200 V/6 A SJT (see Fig. 5b) are at their combined lowest values.

## Figure 5 (a): Simplified circuit schematic of the two-voltage level gate driver developed for driving SiC SJTs (b): Effect of external gate capacitance in the two-level driver on a 1200 V/6 A SJT current turn-on and turn-off times and total device energy loss.

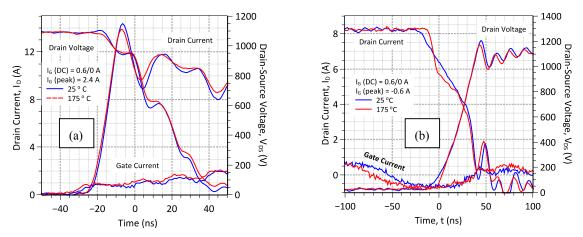

Temperature-independent, low Drain current rise and fall times of 10 ns and 40 ns, respectively, are observed in Fig. 6 during double pulse, inductive-load switching of a 2400 V-class  $3.5 \text{ mm}^2$  SJT at 1100 V and 8 A with a two-voltage level driver. The temperature invarient switching transients confirm minimal conductivity modulation of the n- drift layer, and validate the choice of the unipolar figure of merit used to benchmark the SiC SJTs.

Figure 6 (a) Turn-on and (b) Turn-off waveforms recorded for switching 1100 V and 8 A through a 3.5 mm<sup>2</sup> SiC SJT. There is no difference in switching speed between 25°C and 250°C, due to the unipolar nature of the SJT device design.

#### **Current Gain Stability**

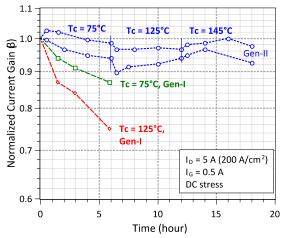

Significant current gain ( $\beta$ ) degradation is typically observed when SiC current-controlled transistors (SJTs or BJTs) are subjected to long-term high-current operation, which remains a key unresolved reliability issue. SiC BJTs or SJTs fabricated even on basal plane dislocation (BPD)-free material are not immune from  $\beta$  degradation, which is attributed to charge trapping by recombination centers in the p-type base layer close to the SiC surface. 1200 V/3.5 mm<sup>2</sup> SiC SJTs fabricated by the Gen-I process displayed a 25% compression of the current gain [5], when subjected to a 6-hour stress with DC drain current of 200 A/cm<sup>2</sup>, gate current of 0.5 A, and a basplate temperature of 125°C. In stark contrast, 1200 V/3.5 mm<sup>2</sup> SJTs fabricated by the Gen-II, high-gain process show within 10%  $\beta$  stability even after stressing at base-plate temperatures as high as 145°C (see Fig. 7), which implies a drastic reduction in the the number of recombination centers, which was also inferred from the minimal emitter-size effect shown in Fig. 3.

Figure 7: Current Gain degradation of several Gen-I and Gen-II, 1200 V/3.5 mm<sup>2</sup> SiC SJTs under a 5 A (DC) drain current and 0.5 A gate current stress at various baseplate temperatures. The current gain of the Gen-II SJT is stable within 10% of its pre-test value after 18 hours of cumulative DC current stress at successively increasing base-plate temperatures from 75°C up to 145°C.

### References

- [1] R. Singh et al. Mater. Sci. Forum, 717-720, pp. 1127-1130 (2012).

- [2] S.G. Sundaresan et al. Proceedings of the 25<sup>th</sup> ISPSD, Kanazawa, Japan, pp.303-306 (2013).

- [3] H. Miyake et al. Mater. Sci. Forum 717-720, pp. 1117-1120 (2012).

- [4] J. Rabkowski et al. IEEE Trans. Electron Dev. 27(5), pp. 2633-2641 (2012).

- [5] S.G. Sundaresan et al. IEEE Trans. Electron Dev. 59(10), pp. 2795-2802 (2012).