### **GeneSiC Semiconductor Reliability Report on**

# **1200 V SiC Junction Transistor (SJT) Devices**

## **Table of Contents**

| 1. Report Summary                | 3 |

|----------------------------------|---|

| 2. Reliability Test Plan         | 3 |

| 3. Reliability Test Descriptions | 4 |

| 4. Device Failure Criteria       | 4 |

| 5. Parameter Verification Data   | 5 |

| 6. Reliability Testing Data      | 6 |

| 7. Conclusion                    | 8 |

|                                  |   |

#### 1. Report Summary

This report summarizes the reliability qualification of GeneSiC Semiconductor 1200 V SiC Junction Transistor (SJT) devices. Theses device come in numerous current ratings and package types. The report includes complete, on-going and planned reliability testing procedures and results.

The reliability standards herein are based on industry standard reference documents the Automotive Electronics Council's (AEC) *Stress Test Qualification for Automotive Grade Discrete Semiconductors* (AEC-Q101, Rev. D) and JEDEC's *Stress-Test-Driven Qualification of Integrated Circuits* (JESD47-I). These two documents reference numerous additional reliability testing standards published by the JEDEC, AEC and MIL-STD.

#### 2. Reliability Test Plan

Table 1 – Reliability test plan summary for 1200 V SJT devices for full AEC-Q101 Qualification.

| Test Name                                             | Test<br>Standard         | Test Conditions                                                                                                     | Test<br>Duration | DUTs                                    |

|-------------------------------------------------------|--------------------------|---------------------------------------------------------------------------------------------------------------------|------------------|-----------------------------------------|

| Pre-Conditioning (PC)                                 | JESD22 A-113             | Prior to select SMD device tests                                                                                    |                  | All SMD Devices                         |

| External Visual (EV)                                  | JESD22 B-101             | Inspect device construction, markings, and workmanship                                                              |                  | All Devices                             |

| Parametric<br>Verification (PV)                       |                          | Test all parameters over entire device temperature range                                                            |                  | 3 Lot X 25 Devices                      |

| High Temperature<br>Reverse Bias (HTRB)               | MIL-STD-750-<br>1 M1038  | $V_R = 960 \text{ V}, T_{amb} = 175 ^{\circ}\text{C}$                                                               | 1000 hr          | 3 Lot X 77 Devices                      |

| High Temperature<br>Gate Bias (HTGB)                  | JESD22 A-108             | $V_{GS} = -25 \text{ V}, T_{amb} = 175 ^{\circ}\text{C}$                                                            | 1000 hr          | 3 Lot X 77 Devices                      |

| Temperature Cycling (TC)                              | JESD22 A-<br>104, App 6  | $T_{amb}$ ramped from -55 °C to 175 °C, 5 min dwell                                                                 | 400 Cycles       | 3 Lot X 77 Devices                      |

| Unbiased Highly<br>Accelerated Stress Test<br>(UHAST) | JESD22 A-118             | $T_{amb}$ = 130 °C, 85 % Relative Humidity                                                                          | 96 hr            | 3 Lot X 77 Devices                      |

| High Humidity and<br>High Temperature Bias<br>(H3TRB) | JESD22 A-101             | $V_R = 100 \text{ V}, T_{amb} = 85 \text{ °C}, 85 \%$ Relative<br>Humidity                                          | 1000 hr          | 3 Lot X 77 Devices                      |

| Intermittent Operating<br>Life (IOL)                  | MIL-STD-750-<br>1 M1037  | 15 000 Cycles, $I_D = 6$ A for 60 s until $\Delta T_i$<br>= 100 °C, then remove bias for 180 s until $T_i = 25$ °C* | 1000 hr          | 3 Lot X 77 Devices                      |

| Wire Bond Integrity<br>(WBI)                          | MIL-STD-750-<br>2 M2037  | $T_{amb}$ = 175 °C, Decapsulate and wire pull inspect all wire bonds                                                | 500 hr           | 3 Lot X 5 Devices                       |

| ESD Human Body<br>Model (HBM)                         | AEC-Q101-<br>001         |                                                                                                                     |                  | 1 Lot X 30 Devices                      |

| ESD Charged Device<br>Model (CDM)                     | AEC-Q101-<br>005         |                                                                                                                     |                  | 1 Lot X 30 Devices                      |

| Destructive Physical<br>Analysis (DPA)                | AEC-Q101-<br>004, Sec. 4 | 50 X Magnification inspection for physical defects                                                                  |                  | 3 Lot X 2 Devices (TC and H3TRB Device) |

$\ast$  Conditions given for 1200 V / 6 A SJT devices, bias conditions will vary by device current rating and package thermal characteristics.

#### **3.** Reliability Test Descriptions

Pre-Conditioning (PC) - SMD parts qualification parts prior to TC, H3TRB & IOL Testing.

**External Visual (EV)** – Visible inspection of device construction and workmanship to ensure that it is in working order prior to testing.

**Parametric Verification (PV)** – Testing of tracked device parameters ( $V_{DS(BD)}$ ,  $I_{DSS}$ ,  $I_{SG}$ ,  $V_{DS(on)}$ , and  $\beta$ ) over rated temperature range prior to testing to ensure statistical compliance of devices within rated datasheet parameters.

**High Temperature Reverse Bias (HTRB)** – Test of the blocking reliability of semiconductor device while enduring the device's maximum rated temperature to ensure there is no decrease in blocking voltage or major increase in reverse bias leakage current.

**High Temperature Gate Bias (HTGB)** – Application of bias to transistor device gate while device is off under maximum rated temperature to test reliability of device current gain.

**Temperature Cycling (TC)** – Cycling of device ambient temperature primarily to ensure reliable packaging of device that will endure device's rated temperature range without degrading which would decrease the power handling capability of the device.

**Unbiased Highly Accelerated Stress Test (UHAST)** – Devices subjected to an extreme environment without electrical bias to ensure protection from pressurized heated moisture by its packaging.

**High Humidity and High Temperature Bias (H3TRB)** – Application of low reverse bias voltage within extreme heated, moist environment to ensure device reliance against electrical short circuit during stress.

**Intermittent Operating Life (IOL)** – Temperature cycling of devices due to self generated heating power from forward biasing without heat sinking ensuring semiconductor and packaging reliability in response to high temperature forward current conduction.

**Wire-Bond Integrity (WBI)** – Test of device wire bond reliability after maximum temperature stress to ensure current handling capability and ensure proper packaging of device.

**Electro Static Discharge Characterization (ESD)** – Test of device properties after subjection of ESD charge to ensure durability of device parameters through ESD events.

#### 4. Device Failure Criteria

Every device has five monitored device parameters (MDP), listed in **Table 2**, measured prior to and immediately following stress testing. Devices are deemed to have failed if a shift of greater than 20 % occurs from pre-test values of any of three MDPs measured prior to and after completion of the reliability stress experiments listed in the previous sections. A device shall also be deemed a failure if the drain leakage current at peak reverse bias increases by greater than 500 % for dry conditions or more than 1000 % in humid conditions. Final MDP values for each device also must be within the device's datasheet minimum and maximum values, or it is a

failure. Testing stess may be intermittently broken as allowed by specific test standards to allow device measurement for completeness of results as desired.

| Monitored Device<br>Parameters  |                     | Measurement Condition                         | Failure Criteria    |

|---------------------------------|---------------------|-----------------------------------------------|---------------------|

| Breakdown Voltage               | $V_{DS(BD)}$        | $I_{DSS} = 1 \text{mA}, V_{GS} = 0 \text{ V}$ | $> \pm 20$ % Change |

| Leakage Current                 | I <sub>DSS</sub>    | $V_{DS} = 1200 V, V_{GS} = 0 V$               | > 500 % Increase    |

| Reverse Gate Leakage<br>Current | I <sub>SG</sub>     | $V_{SG} = 10 \text{ V}$ , Open Drain          | > 500 % Increase    |

| Forward Voltage Drop            | V <sub>DS(on)</sub> | $I_D = Rated Current, I_{GS} = 500$ mA        | $> \pm 20$ % Change |

| Current Gain                    | β                   | $I_D$ = Rated Current, $V_{DS}$ = 5 V         | $> \pm 20$ % Change |

Table 2 – Identification of SJT Monitored Device Parameters (MDP) and measurement conditions.

#### 5. Parameter Verification Data

V

\_

V<sub>DS(on)</sub>

Parameter verification (PV) data are shown with Monitored Device Parameter (MDP) ( $V_{DS(BD)}$ ,  $I_{DSS}$ ,  $I_{SG}$ ,  $V_{DS(on)}$ , and  $\beta$ ) characterization done prior to reliability testing to ensure statistical compliance of devices within rated datasheet parameters (the upper or lower specified limit, LSL or USL). The process capability index (Cpk) of each MDP is also given.

**Parameter** Spec Spec St. Unit Min Max Mean C<sub>pk</sub> V 1200 1205.0 1675.0 1340.56 68.18 0.687 V<sub>DS(BD)</sub> \_ 50 0.01 9.27 0.61 11.54 I<sub>DSS</sub> μA 1.42 \_ ISG nA \_ 10 0.82 1.04 0.93 0.05 56.08 β 45 45.7 \_ 60.83 53.43 4.41 0.636 \_

1.19

1.65

1.37

0.09

2.323

Table 3 – Parameter verification (PV) data of all 1200 V SJT devices measured at 25 °C.

2.0

#### 6. Reliability Testing Data

The most recently available reliability testing data are presented in this section. All reliability testing is constantly on-going and results will continue to be updated regularly. To date, no devices failures have been observed in any GeneSiC device for any test. Test data currently includes EV, PV, HTRB, HTGB, TC, UHAST, and IOL tests. The results are shown in

**Table 4**. Additional graphical data are also reported pertaining to the HTRB and HTGB reliability of the 1200 V devices

| Table 4 – Current reliability test data of all 1200 V SJT devices measured to-date with no failures |

|-----------------------------------------------------------------------------------------------------|

| recorded.                                                                                           |

| Test Name | <b>Testing Time to Date</b> | <b>Devices Tested</b> | <b>Device Failures</b> |

|-----------|-----------------------------|-----------------------|------------------------|

| EV        | _                           | All Devices           | 0                      |

| PV        | _                           | All Devices           | 0                      |

| HTRB      | 1000 hr                     | 22                    | 0                      |

| HTGB      | 1000 hr                     | 10                    | 0                      |

| TC        | 305 Cycles                  | 30                    | 0                      |

| UHAST     | 96 hr                       | 30                    | 0                      |

| IOL       | 303 Cycles                  | 5                     | 0                      |

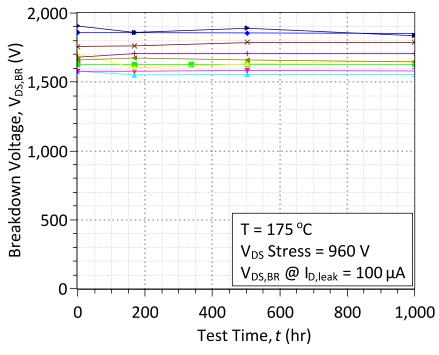

Figure 1 – Breakdown voltage  $V_{DS,BR}$  of representative SJTs measured during MIL-STD high-temperature reverse bias (HTRB) testing showing no degradation due to stress.  $V_{DS,BR}$  is taken where drain-source leakage current equals 100 uA. This device-under-test is representative of all GeneSiC SJT devices tested.

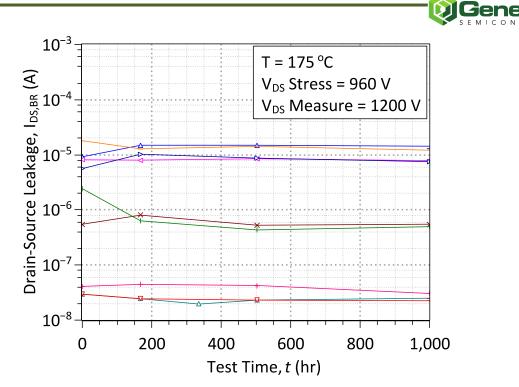

Figure 2 – Drain-source leakage current  $I_{DS,BR}$  of representative SJTs measured during MIL-STD hightemperature reverse bias (HTRB) testing showing no degradation due to stress.  $I_{DS,BR}$  is taken at nominal rated drain-source breakdown voltage  $V_{DS} = 1200$  V. These devices-under-test are representative of all GeneSiC SJT devices tested.

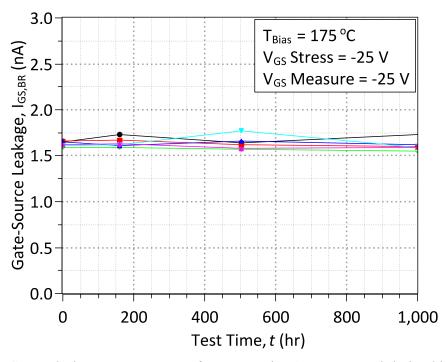

Figure 3 – Gate-Source leakage current  $I_{GS,BR}$  of representative SJTs measured during high-temperature gate bias (HTGB) testing showing no degradation due to stress.  $I_{GS,BR}$  is taken at gate-source voltage  $V_{GS} = -25$  V.

#### 7. Conclusion

This report summarizes GeneSiC Semiconductor's comprehensive reliability test plan for their 1200 V SiC Junction Transistor (SJT) devices based on AEC, JEDEC, and MIL-STD standards. A comprehensive list of devices covered by this report can be seen on the GeneSiC website\*. Reliability testing of these devices is constantly being performed to meet these certifications. Thus far, **zero GeneSiC Semiconductor devices have failed any reliability test to-date** and all devices have thus far met GeneSiC internal reliability requirements. This document will continue to be updated occasionally to show the most current reliability data available.

\* http://www.genesicsemi.com/index.php/sic-products/sjt