# A 10-kV Large-Area 4H-SiC Power DMOSFET With Stable Subthreshold Behavior Independent of Temperature

Robert S. Howell, *Member, IEEE*, Steven Buchoff, Stephen Van Campen, *Member, IEEE*, Ty R. McNutt, *Member, IEEE*, Andris Ezis, *Senior Member, IEEE*, Bettina Nechay, *Member, IEEE*, Christopher F. Kirby, *Member, IEEE*, Marc E. Sherwin, *Member, IEEE*, R. Chris Clarke, *Fellow, IEEE*, and Ranbir Singh, *Member, IEEE*

Abstract—This paper presents the development and demonstration of large-area 10-kV 4H-SiC DMOSFETs that maintain a classically stable low-leakage normally off subthreshold characteristic when operated at  $\leq 200~^{\circ}\text{C}$ . This is achieved by an additional growth (epitaxial regrowth) of a thin epitaxial layer on top of already implanted p-well regions in conjunction with a N2O-based gate oxidation process. Additionally, the design space of the DMOSFET structure was explored using analytical and numerical modeling together with experimental verification. The resulting 0.15-cm² active 0.43-cm² die DMOSFET with 10-kV breakdown provides  $I_{\rm DS}=8~{\rm A}$  at a gate field of 3 MV/cm, along with a subthreshold current at  $V_{\rm GS}=0~{\rm V}$  that decreases from 1  $\mu{\rm A}~(6.7~\mu{\rm A/cm}^2)$  at 25  $^{\circ}{\rm C}$  to 0.4  $\mu{\rm A}~(2.7~\mu{\rm A/cm}^2)$  at 200  $^{\circ}{\rm C}$ .

Index Terms—Power MOSFETs, power switching, silicon carbide, subthreshold behavior.

### I. Introduction

F GREAT interest for high-voltage (10+kV) switching applications is the 4H-SiC DMOSFET because it combines the high-breakdown low specific on-resistance of the 4H-SiC drift region with the majority carrier operation of the MOSFET, thereby accruing both low switching losses and the uniform current distribution needed for device paralleling. These attributes have made the 4H-SiC DMOSFET attractive as a potential candidate for insertion into future 10+kV power switching architectures [1]. The lower switching losses of the SiC DMOSFET allow the architectures to be designed around higher frequencies ( $\geq 20~kHz$ ), substantially reducing the overall system size and weight of solid-state power switching applications.

Significant effort has been made in the development of 4H-SiC DMOSFETs, primarily in the 1+-kV range, including work on optimizing the design of the DMOSFET structure [2]. However, because of their thinner drift layers and low specific

Manuscript received November 29, 2007; revised May 1, 2008 and May 21, 2008. This work was supported by Office of Naval Research Contract N00014-05-C-0203 under contract monitor Dr. Harry Dietrich. The review of this paper was arranged by Editor J. Cooper.

R. S. Howell, S. Buchoff, S. Van Campen, T. R. McNutt, A. Ezis, B. Nechay, C. F. Kirby, M. E. Sherwin, and R. C. Clarke are with Northrop Grumman Corporation, Linthicum, MD 21090 USA (e-mail: rs.howell@ngc.com).

R. Singh is with GeneSiC Semiconductor Inc., Dulles, VA 20166 USA. Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TED.2008.928204

on-resistances, these lower voltage SiC DMOSFETs are smaller in area and have different equivalent circuit design considerations than used with 10-kV SiC DMOSFETs. The 10-kV SiC DMOSFETs have recently been scaled up in current output, with die sizes increasing from 0.11 cm<sup>2</sup> (0.0476-cm<sup>2</sup> active area) to 0.3 cm<sup>2</sup> (0.15-cm<sup>2</sup> active area) reported, capable of 5–10 A at room temperature [3], [4]. In addition to these useful improvements in blocking voltage and ON-state current, it is essential that DMOSFETs demonstrate a stable subthreshold characteristic over the projected operating temperature range  $(\leq 200 \, ^{\circ}\text{C})$ . This is critical in order to satisfy the need for both a normally off device and a device with an OFF-state leakage that does not compromise its blocking voltage at higher temperatures. The large-area SiC DMOSFETs reported in the literature, which have provided their subthreshold behavior as a function of temperature, have tended to become normally on or have excessive OFF-state leakage when operated at high (> 150 °C) temperatures due to an apparent temperature-dependent fixed charge voltage shift in their subthreshold characteristic [5].

In order to create a viable 10+-kV SiC MOSFET, a robust process is required that achieves a sustainable yield of large-area devices that have low-leakage normally off subthreshold characteristics above 150 °C. In this paper, we report on the successful development and demonstration of such a large-area 10+-kV SiC MOSFET process.

### II. DESIGN CONSIDERATIONS

The fabrication of 4H-SiC DMOSFETs in the 10+-kV range poses particular challenges resulting from the limitations of currently available SiC material quality and the required thick ( $\sim 100~\mu m$ ) drift region to achieve 10+kV, competing with the need for large-area devices. As the power switching modules that would use these 10-kV devices are specified to carry over a hundred amperes, even paralleling several DMOSFET parts in each module still requires each DMOSFET die to have a large active area in addition to a large area devoted to junction termination extension (JTE) that allows 10+-kV breakdown. For example, at room temperature, a  $100-\mu m$  drift region doped at  $5\times 10^{14}~cm^{-3}$  that is appropriate for 10-kV blocking will have a specific on-resistance of  $133~m\Omega \cdot cm^2$ . Thus, considering the drift resistance alone, a 10-A part in a package capable of removing  $750~W/cm^2$  of waste heat from the part would

require at least an active area of 0.133 cm<sup>2</sup>, and when the effects of self-heating at elevated power levels are considered, an even larger active area would be required to maintain the 10-A current level and thereby compensate for the increased drift resistance associated with the inverse relationship between carrier mobility and temperature. However, using 0.133-cm<sup>2</sup> active area as a baseline and if the active area is a square with a lateral JTE length of 500  $\mu$ m, the final die size would then be 0.216 cm<sup>2</sup>. Large die areas such as this suffer from a pronounced sensitivity to the defect density in the 4H-SiC material, creating substantial challenges in developing robust processes that have useful yields of 10-kV devices. This has been previously illustrated even at the 1-kV level, as 1200-V 4H-SiC vertical JFETs have been reported to have a decrease in their observed breakdown voltage with respect to the theoretical maximum allowed by the drift conditions, from 93% for VJFETs with  $1.23 \times 10^{-3}$ -cm<sup>2</sup> active areas to 91% for 0.068-cm<sup>2</sup> active areas [6], [7].

These problems are in addition to the requirement that 4H-SiC MOSFETs maintain normally off behavior as a function of temperature. If, as has been observed [5], the subthreshold behavior shifts toward a normally ON-state as a function of increasing operating temperature, even if the device remains normally off (i.e., a positive threshold voltage), the increase in OFF-state leakage associated with the shifting subthreshold region can dramatically reduce the breakdown voltage of the device independent of the JTE design.

In order to ameliorate these issues, a successful large-area 10+-kV MOSFET is required to employ a higher degree of margin in the design rules and process techniques than used for lower voltage material. An example of this is in the choice of drift thickness and doping. Assuming the adoption of a punchthrough structure, a theoretical 10-kV breakdown could be achieved with a 75- $\mu$ m-thick drift doped at  $9 \times 10^{14}$  cm<sup>-3</sup>, with a specific on-resistance of only 57 m $\Omega \cdot \text{cm}^2$ , which is less than half the specific on-resistance of drifts actually used in 10-kV devices. The reason for the difference is twofold: 1) The defects inherent in the material reduce the achievable breakdown voltage of the device, a problem exacerbated for larger devices which contain more defects, and 2) variations in thickness and doping of epitaxially grown films necessitate conservative specifications for these films in order to ensure that the resulting drift layer will be capable of blocking the desired voltage.

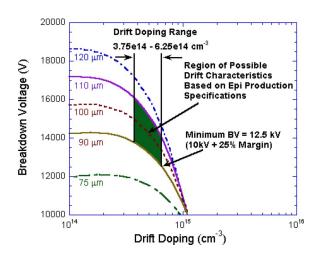

Fig. 1 shows an analytical model of the breakdown for a 4H-SiC punchthrough drift structure as a function of thickness and doping level. Given the presence of defects and limitations on JTE design due to process variance, an at least 25% margin above the 10-kV range is desirable to maximize the likelihood of achieving 10-kV MOSFETs with reasonable yield. Additionally, the epitaxial vendor was only able to specify doping within  $\pm 25\%$  and thickness within  $\pm 10\%$  for this region of thick, low doped drift. Thus, Fig. 1 highlights the resulting region for a nominally 100- $\mu$ m layer doped at  $5\times 10^{14}$  cm $^{-3}$ , becoming 90–110  $\mu$ m and  $3.75\times 10^{14}$ – $6.25\times 10^{14}$  cm $^{-3}$  based on these error bars, respectively, and shows that the minimum breakdown for this process space is 12.5 kV, incorporating the desired 25% margin above 10 kV.

Fig. 1. Analytical model of breakdown voltage for a SiC punchthrough drift region nominally doped at  $45\times10^{14}~{\rm cm^{-3}~(\pm25\%)}$  and 100  $\mu m~(\pm10\%)$  thick, appropriate for 10-kV operation with a 25% margin.

Having defined an appropriate drift region thickness and doping to meet the OFF-state blocking, the ON-state properties still require optimization, involving both the MOS channel characteristics (mobility, threshold voltage, etc.) and the physical layout of the device. Unlike 1+-kV SiC DMOSFETs which are very sensitive to channel resistance and channel mobility, the higher resistance of the drift in 10-kV DMOSFETs makes the channel resistance and mobility much less of a contributor to the total device on-resistance. DMOSFETs of 10 kV do, however, share a common sensitivity to threshold voltage and subthreshold stability as a function of temperature. It has been observed, however, that SiC MOS channels of higher mobility and lower resistance, which are formed using an NO oxidation method, have low and even normally on threshold voltages, as well as subthreshold characteristics that shift toward a leaky state as temperature increases [5]. For this reason, a twofold approach to stabilizing the threshold voltage as a function of temperature was taken. First, the channel performance was improved using an epitaxial regrowth (performed at Northrop Grumman Corporation) above the implanted p-well region in conjunction with a N2O gate oxidation process. The use of a similar epitaxial regrowth layer above the implanted p-well has previously been shown to improve the channel resistance [8], [9] and, in this paper, is shown to also improve the subthreshold/temperature characteristics. The second aspect was to design and fabricate an array of small-area DMOSFETs in order to pragmatically explore the device geometry design space.

### III. EXPERIMENTAL DETERMINATION OF CHANNEL PROCESS AND DEVICE GEOMETRIES

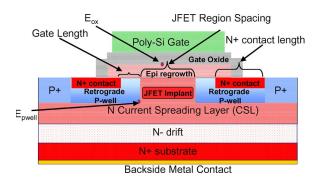

Efforts to explore the 10-kV DMOSFET geometry design space and the channel process were performed in parallel, to be combined together in an optimized large-area device after obtaining the results from both experimental thrusts. The design space optimization focused on the pitch of the DMOSFET cell, examining gate length, JFET spacing, and N+ source contact length effects on the device performance. Fig. 2 shows a representative cross section of the DMOSFET, with the various regions of interest being highlighted. A short gate length

Fig. 2. DMOSFET cross-sectional view, showing the device geometries that were varied experimentally and points where  $E_{\rm ox}$  and  $E_{\rm pwell}$  were calculated in numerical simulation.

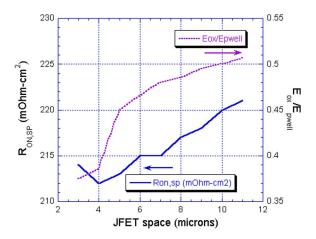

Fig. 3. Analytical model of specific on-resistance and  $E_{\rm ox}/E_{\rm pwell}$  plotted against JFET spacing. The model assumes a low-doped 100- $\mu$ m drift and a 1- $\mu$ m (1  $\times$  10<sup>16</sup>-cm<sup>2</sup>) CSL.

can substantially reduce the channel resistance, but this has a limited benefit to the overall on-resistance of 10-kV devices because of their high drift resistance and must be counterbalanced by concerns of possible problems associated with shortchannel devices, such as drain-induced barrier lowering causing premature breakdown. This factor motivated an exploration of gate lengths of 1.0 and 1.5  $\mu$ m in addition to a channel length of  $0.5 \mu m$ . The JFET spacing is a critical parameter, as too small of a spacing will increase resistance by impeding all current flow, whereas too large of a JFET space not only hurts onresistance by increasing the device pitch but also increases the electric field seen by the gate oxide above the JFET region, causing reliability issues. Fig. 3 shows a numerical model of this effect, with specific on-resistance and  $E_{\rm ox}/E_{\rm pwell}$  (the ratio of the electric field in the gate oxide interface at the center of the cell to the field seen at the bottom corner of the p-well) plotted as a function of JFET spacing. This model shows a minimum in specific on-resistance with a 4- $\mu$ m JFET space, whereas the corresponding experimental design space included JFET spacings of 4, 5, and 6  $\mu$ m. It should be noted that, in addition to the low-doped thick drift layer needed for 10-kV devices, the numerical model assumes the use of a 1- $\mu$ mthick current spreading layer (CSL) doped at  $1 \times 10^{16}$  cm<sup>-3</sup>. This CSL layer is essential for allowing the current to spread underneath the p-well region prior to entering the low-doped drift and minimizing the spreading resistance of the device and

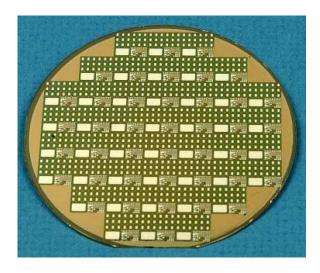

Fig. 4. Image of the completed wafer with 18 DMOSFET geometry variations per reticle.

is also a major factor in determining the JFET resistance of the device. To further explore the impact of the doping level in the CSL/JFET, an additional experimental split was incorporated to implant one wafer with nitrogen (at 195 keV and  $2.6\times10^{12}\text{-cm}^{-2}$  dose) to create a buried  $1\times10^{17}~\text{cm}^{-3}$  region in the JFET space. The last variable was the source contact length, which is desired to be small to increase device pitch but large enough that source contact resistance is negligible.

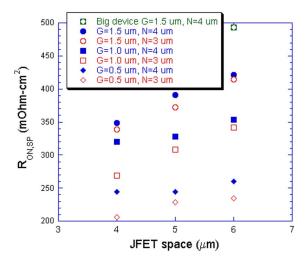

Two 4H-SiC wafers were processed with these interleaved design splits, creating 18 different small-area device designs (each with an active area of 0.0029 cm<sup>2</sup>) in each reticle, with an additional 19th larger-area device (0.07-cm<sup>2</sup> active area) that used the largest design rules and filled the remaining available space on the reticle. One wafer received the aforementioned JFET implant while the other did not, and all other processes remained identical for both wafers. The starting wafers used a 100- $\mu$ m epitaxial layer doped at  $5 \times 10^{14}$  cm<sup>-3</sup>, along with a  $1-\mu m$  1 ×  $10^{16}$ -cm<sup>-3</sup> CSL, and the p-wells were formed with a retrograde implantation of aluminum. The gate oxide was formed using N<sub>2</sub>O, creating a 400-Å-thick layer. Because the channel optimization work was being performed in parallel with this experiment, these wafers did not use the epitaxial regrowth process above the implanted p-well. The channel length was defined using standard stepper lithography, comprising the spacing between the edges of the n+ and p-well implants, respectively, down to a length of 0.5  $\mu$ m without the use of selfaligned techniques. The p+ contact to the p-well was 0.75  $\mu$ m wide. An n-type doped polysilicon gate was used with a 0.5- $\mu m$ overlap above the n+ region. The source contacts were formed using nickel silicide, whereas an aluminum layer formed the final metallization. Fig. 4 shows an image of a completed wafer, and Fig. 5 shows the averaged specific on-resistances for all devices on the wafer without the additional JFET implantation. While the primary driver of resistance was the gate length and total device pitch, no adverse affect on breakdown was observed for the shorter channel devices. Likewise, the ON-state resistances decreased with JFET spacing and N+ source contact length. The "Big" device on the reticle had a larger specific on-resistance because its size allowed it to benefit less from the

Fig. 5. Specific on-resistances for the 10-kV DMOSFET geometry design space experiment.

Fig. 6. Histogram of specific on-resistance for the smallest geometry devices (JFET space  $=4~\mu m,~gate~length=0.5~\mu m,~and~N+~source~length=3~\mu m)$  for the wafer with and without a JFET implantation.

spreading current through the low-doped drift region compared to the small DMOSFETs. The conclusion reached from these results was that the smaller geometries explored were not detrimental to OFF-state performance but could be used to take advantage of the resulting minimized on-resistance.

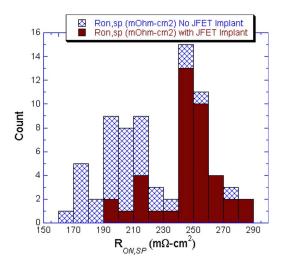

Because the wafer without the JFET implant showed negligible JFET resistance, it was expected that the simultaneously processed wafer with the JFET implant would show similar results. However, the wafer with the JFET implant demonstrated remarkably higher resistances across all devices. Fig. 6 shows a histogram of the specific on-resistances for all of the smallest geometry devices on both wafers (JFET space = 4  $\mu m$ , gate length = 0.5  $\mu m$ , and N+ source length = 3  $\mu m$ ). The mean specific on-resistance of these devices on the wafer without the JFET implant was 209 m $\Omega \cdot cm^2$ , but 248 m $\Omega \cdot cm^2$  was observed for the wafer with the JFET implant. As the on-wafer lateral MOSFET test structures showed very similar mobility results for both wafers and, according to the data received from the vendor, the wafers' drift doping and thickness values were virtually identical, the variation between results is

Fig. 7. (a) Histogram of mobilities for W/L=100- $\mu m/100$ - $\mu m$  devices grown on a wafer with p-epitaxy, a wafer with an implanted p-well, and a wafer with an epitaxial regrowth on top of an implanted p-well. (b) Histogram of  $V_{\rm TH}$  for W/L=100- $\mu m/100$ - $\mu m$  devices grown on a wafer with p-epitaxy, a wafer with an implanted p-well, and a wafer with an epitaxial regrowth on top of an implanted p-well.

attributed to the act of implantation itself. It is hypothesized that the JFET implantation caused a significant amount of damage that was not removed during the implant anneal process.

In parallel with the DMOSFET geometry optimization, small lateral MOSFETs were also being created to optimize the MOS channel characteristics. It was hypothesized that the damage from the implanted p-well could not be fully removed during the activation annealing. An epitaxial layer grown after the implant, however, could serve to move the channel away from this damage and significantly improve device performance. Additionally, a N<sub>2</sub>O gate oxidation process could be employed, which does not have the same rigorous safety requirements that accompany the commercial use of NO and is thus easier to implement.

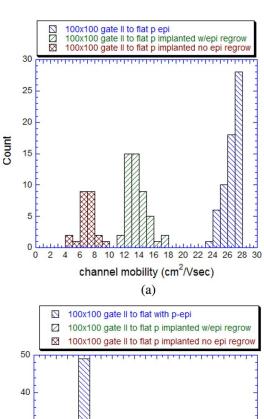

Fig. 7(a) shows a histogram of mobilities measured on the lateral MOSFETs ( $W/L=100~\mu\mathrm{m}/100~\mu\mathrm{m}$ ) from three

Fig. 8.  $I_{\rm DS}$  and transconductance mobility plots as a function of  $V_{\rm GS}$  for representative 100- $\mu \rm m/100$ - $\mu \rm m$  MOSFETs with implanted p-wells and with or without an epitaxial regrowth process.

different SiC wafers. All wafers used similar process sequences, including the N<sub>2</sub>O gate oxide formation, with the exception that one wafer formed the devices on a 5- $\mu$ m p-epitaxial layer, whereas the other two used aluminum-implanted p-wells. Of these two implanted p-well wafers, one, in turn, received an epitaxial regrowth process, growing  $\sim 700$  Å above the p-well. The histogram shows distinct populations for each of the process conditions, with the implanted p-well alone greatly decreasing the mobility of the devices compared to the undamaged epitaxial p-layer. The addition of the epitaxial regrowth has essentially doubled the measured mobility of devices on an implanted p-well, although still being only about half the mobility of the "ideal" case of the devices on the p-epitaxial material. In a similar fashion, the  $V_{\mathrm{TH}}$  of the devices has been lowered by the incorporation of the epitaxial regrowth, with the histogram in Fig. 7(b) showing the highest  $V_{\rm TH}$  for devices on an implanted p-well and the incorporation of an epitaxial regrowth acting to decrease the  $V_{\rm TH}$  by approximately 2 V. The devices on the p-epitaxial material, with the least damage and associated fixed charge, have the population with the lowest  $V_{\rm TH}$ .

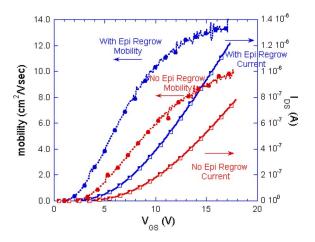

Fig. 8 shows the  $I_{\rm DS}$  versus  $V_{\rm GS}$  behavior of two representative devices on implanted p-wells, comparing current and transconductance values between devices with and without the epitaxial regrowth process. When using the epitaxial regrowth, the mobility has nearly doubled, increasing from a peak of 9.8 to 13.2 cm²/V · s, and the current has increased by a factor of approximately 1.7 times due to both the increase in mobility and the reduction in  $V_{\rm TH}$ . This performance, while not generating as high values of channel mobilities as an NO process, is sufficient for the needs of a 10-kV DMOSFET process, and these results were combined with the results from the device geometry experiment to create an optimum design for large-area 10-kV DMOSFETs.

## IV. FABRICATION AND MEASUREMENTS OF LARGE-AREA DMOSFETS

Incorporating the results of the optimization experiments, large-area 10-kV DMOSFETs were fabricated. Of those

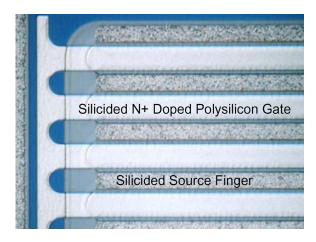

Fig. 9. Image of a portion of the fabricated  $0.15\text{-cm}^2$  active  $(0.43\text{-cm}^2\text{ chip})$  area) DMOSFET with a gate length of  $0.5~\mu\text{m}$  and a pitch of  $10~\mu\text{m}$ .

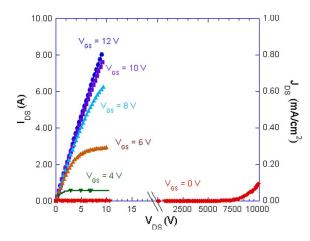

Fig. 10. ON-state and breakdown characteristics of a  $0.15\text{-cm}^2$  active  $0.43\text{-cm}^2$  chip-area DMOSFET.

fabricated, the most promising design used a gate length of 0.5  $\mu$ m in a cell pitch of 10  $\mu$ m. The drift remained 5 × 10<sup>14</sup> cm<sup>-3</sup> and 100  $\mu$ m thick, with a 1- $\mu$ m 1 × 10<sup>16</sup> cm<sup>-3</sup> CSL, and a mesa etch process was used to etch around the active area of the device through the CSL and to the drift region. A retrograde Al-implanted p-well was used with an epitaxial regrowth layer of ~1000 Å, followed by a N<sub>2</sub>O gate oxide process forming a 400-Å-thick layer. A N+ doped polysilicon gate was used with a self-aligned nickel silicidation process, and the source contacts were also formed using nickel silicide. A three-zone JTE was used with an extent of 750  $\mu$ m, and the resulting chip was 0.42 cm<sup>2</sup>, with a 0.15-cm<sup>2</sup> active area. Fig. 9 shows an image of the device fingers prior to final passivation and metallization, showing the linear cell design.

The forward I-V and corresponding reverse breakdown J-V for one of these devices is shown in Fig. 10. With 12 V applied to the gate (3 MV/cm), this device achieved 8 A at 9 V  $V_{\rm DS}$  and a current density of 53 A/cm² while generating 480-W/cm² waste heat, which is well below the reasonable limit of 750 W/cm² for current packaging technology that uses liquid cooling [10]. The breakdown voltage of this device is excellent, with only 0.1 mA/cm² of leakage at 10 kV and demonstrating the breakdown margin built into the device that

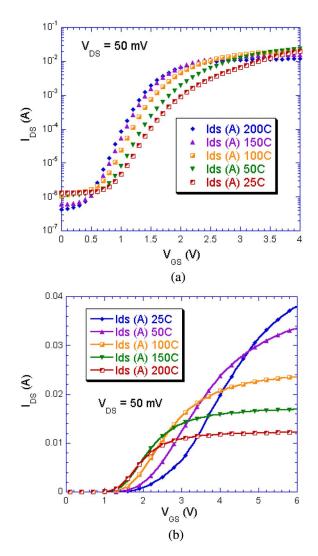

Fig. 11. (a)  $I_{\rm DS}-V_{\rm GS}$  subthreshold characteristics of a 0.15-cm<sup>2</sup> active 0.43-cm<sup>2</sup> chip-area DMOSFET across a 25–200 °C temperature range. (b)  $I_{\rm DS}-V_{\rm GS}$  linear characteristics of a 0.15-cm<sup>2</sup> active 0.43-cm<sup>2</sup> chip-area DMOSFET across a 25–200 °C temperature range.

was previously described in Section II. The leakage current does begin to increase after 7500 V, as minor defects within the SiC epitaxial structure allow the beginning of avalanche breakdown.

The measured temperature response of the device is also excellent, with no shifting of its subthreshold current as a function of temperature. Fig. 11 shows the  $I_{\rm DS}$  versus  $V_{\rm GS}$  of this device for temperatures ranging from 25 °C to 200 °C and for  $V_{\rm DS}=50$  mV. As the temperature increases, the threshold voltage decreases, but that is due to the increasing sharpness of the subthreshold characteristic, and there is no appearance of a charge-induced shift in the subthreshold current. The subthreshold swing S is shown by Sze [11] to be

$$S = \frac{kT}{q} \ln 10 \cdot \left( 1 + \frac{C_D}{C_{\text{ox}}} \right) \cdot \frac{1 + \left( \left( C_D + qD_{\text{it}} \right) / C_{\text{ox}} \right)}{1 + \left( C_D / C_{\text{ox}} \right)}$$

(1)

where  $C_D$  is the depletion capacitance,  $C_{\rm ox}$  is the oxide capacitance, and  $D_{\rm it}$  is the interface trap density. A steeper subthreshold I-V characteristics equates to a lower S, and MOSFETs

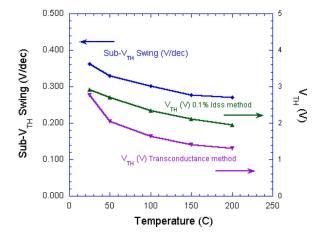

Fig. 12. Measured subthreshold swing and threshold voltage as a function of temperature for the  $0.15\text{-cm}^2$  active  $0.43\text{-cm}^2$  chip-area DMOSFET across a  $25\text{--}200~^\circ\text{C}$  temperature range.

with high levels of interface traps, as is common for SiC, have increased values for subthreshold swings and shallower subthreshold I-V characteristics. The increasing subthreshold slope and decreasing swing observed in Fig. 11 indicate a significant decrease in  $D_{\rm it}$  with temperature, particularly because an increase in temperature by itself acts to increase S.

Aside from the subthreshold swing, the other major characteristic associated with this region is the possibility of a charge-induced shift. This normally occurs due to fixed charge and is observed in lateral shifts in the subthreshold I-V characteristics and corresponding shifts in threshold voltage by the relationship  $V_{\rm shift} = -Q_{\rm fixed}/C_{\rm ox}$ . In SiC MOSFETs, this fixed shift has been observed to have an additional temperature dependency, with the shift appearing as temperature is increased [5].

The presence of a temperature-controlled charge-induced lateral shift in the subthreshold characteristics would cause the device to begin to turn on as temperature increased, despite the gate remaining at 0 V. In contrast, the device shown in Fig. 11 has a leakage current (at  $V_{\rm DS} = 50~{\rm mV}$ ) that decreases with increasing temperature, from 1  $\mu$ A (6.7  $\mu$ A/cm<sup>2</sup>) at  $V_{\rm GS}=0~{\rm V}$  and 25 °C to 0.4  $\mu{\rm A}$  (2.7  $\mu{\rm A/cm^2}$ ) at  $V_{\rm GS}=0~{\rm V}$ and 200 °C. Because this device does not experience a chargeinduced lateral shift on the  $I_{\rm DS}$ - $V_{\rm GS}$  curve as a function of temperature, there is no additional contribution to the avalanche breakdown current at higher temperatures from an undesirable temperature-controlled partial turn-on of the device that could otherwise significantly lower the resulting breakdown voltage. Fig. 12 shows the subthreshold swing and threshold voltage of the device as a function of temperature, with the threshold voltage being plotted as determined by the transconductance method and as defined by the point where the drain current is equal to 0.1% of the maximum current. The threshold voltage tracks the subthreshold swing values, as it decreases due to the steepening of the slope, which is caused by the filling of traps at higher temperature with the higher numbers of intrinsic carriers.

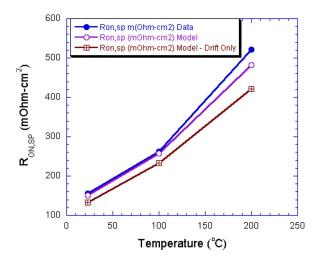

The specific on-resistance of the device has also been evaluated, as shown in Fig. 13, with the experimental data being compared to an analytical model of the DMOSFET presented

Fig. 13. Measured specific on-resistance for the 0.15-cm<sup>2</sup> active 0.43-cm<sup>2</sup> chip-area DMOSFET across a 25–200-°C temperature range as a function of temperature compared to the analytical model.

Fig. 14. Stressing of DMOSFET with epitaxial regrowth layer on p-well implant. Stressed at  $V_{\rm GS}=12$  V (3 MV/cm) and  $V_{\rm DS}=12.5$  V.

by Baliga [12]. The primary component of the device resistance remains the drift resistance, with the MOS channel and the rest of the device components forming 15%–20% of the total device resistance. The initial impact of heating is minimized as traps are filled to counteract the normal decrease in mobility for majority carrier devices, which is why the proportion of resistance in the MOS channel does not substantially increase until the 200-°C data point. A corresponding lateral MOSFET was measured with mobilities of 13, 10, and 3.2 cm²/V·s at 27 °C, 100 °C, and 200 °C, respectively, demonstrating this impact.

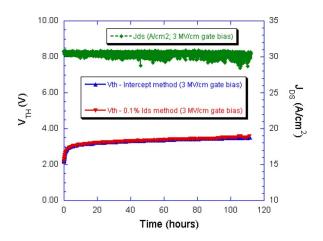

These DMOSFETs have also shown excellent preliminary operational stability as a function of temperature. Fig. 14 shows the results of temperature–bias stress testing on a small-area (0.0029 cm² active) test DMOSFET with identical design rules and made simultaneously with the large-area DMOSFET. The device was stressed at  $V_{\rm GS}=12~\rm V$  (3 MV/cm) and  $V_{\rm DS}=12.5~\rm V$  on a heated chuck held at 200 °C for a period of over 110 h. The threshold characteristics were measured intermittently throughout the test period, and the output current was monitored continually. After an initial increase in  $V_{\rm TH}$

of 0.8 V after 5 h,  $V_{\rm TH}$  increased by only 0.5 V over the next hundred hours of testing, whereas the output current dropped by 1%.

### V. CONCLUSION

The design and optimization of a large-area 10-kV DMOSFET are presented, with a 0.15-cm² active-area (0.43-cm² die) device providing 8 A at  $V_{\rm DS}=9$  V (53 A/cm² and 480 W/cm²) and 3 MV/cm on the gate oxide. With the incorporation of an epitaxial regrowth layer above the implanted p-well, excellent subthreshold and stressed performance characteristics were demonstrated across the 25–200-°C temperature range. No subthreshold characteristic shift was observed as a function of increased temperature, resulting in a low OFF-state leakage of 0.4  $\mu$ A (2.7  $\mu$ A/cm²) at  $V_{\rm GS}=0$  V and 200 °C.

### ACKNOWLEDGMENT

The authors would like to thank Dr. K. Hobart (NRL) and Dr. A. Hefner (NIST) for their evaluation of the reported devices. This paper was conducted under the DARPA HPE Phase II Program, with S. Beermann-Curtin as the program manager.

#### REFERENCES

- [1] G. Walden, T. McNutt, M. Sherwin, S. Van Campen, R. Singh, and R. Howell, "Comparison of 10 kV 4H-SiC power MOSFETs and IGBTs for high frequency power conversion," in *Proc. ICSCRM*, Otsu, Japan, 2007

- [2] A. Saha and J. A. Cooper, "1-kV 4H-SiC power DMOSFET optimized for low on-resistance," *IEEE Trans. Electron Devices*, vol. 54, no. 10, pp. 2786–2791, Oct. 2007.

- [3] S. Ryu, S. Krishnaswami, M. O'Loughlin, J. Richmond, A. Agarwal, J. Palmour, and A. Hefner, "10-kV, 123 mΩ-cm<sup>2</sup> 4H-SiC power DMOSFETs," *IEEE Electron Device Lett.*, vol. 25, no. 8, pp. 556–558, Aug. 2004.

- [4] S. Ryu, S. Krishnaswami, B. Hull, J. Richmond, A. Agarwal, and A. Hefner, "10 kV, 5A 4H-SiC power DMOSFET," in *Proc. 18th ISPSD*, Naples, Italy, Jun. 4–8, 2006, pp. 265–268.

- [5] A. Agarwal and S. Ryu, "Status of SiC power devices and manufacturing issues," in *Proc. Compound Semicond. MANTECH Conf.*, Vancouver, BC, Canada, Apr. 24–27, 2006, pp. 215–218.

- [6] V. Veliadis, M. McCoy, T. McNutt, H. Hearne, L. S. Chen, G. DeSalvo, C. Clarke, B. Geil, D. Katsis, and C. Scozzie, "Fabrication of a robust high-performance floating guard ring edge termination for power silicon carbide vertical junction field effect transistors," in *Proc. Compound Semicond. MANTECH Conf.*, Austin, TX, May 14–17, 2007, pp. 217–221.

- [7] V. Veliadis, T. McNutt, M. McCoy, H. Hearne, G. DeSalvo, C. Clarke, P. Potyraj, and C. Scozzie, "1200-V, 50-A, silicon carbide vertical junction field effect transistors for power switching applications," in *Proc. ICSCRM*, Otsu, Japan, 2007.

- [8] R. Singh, D. C. Capell, M. K. Das, L. A. Lipkin, and J. W. Palmour, "Development of high current 4H-SiC ACCUFET," *IEEE Trans. Electron Devices*, vol. 50, no. 2, pp. 471–478, Feb. 2003.

- [9] R. Singh, D. C. Capell, J. T. Richmond, and J. W. Palmour, "High channel density, 20 A 4H-SiC ACCUFET with Ron, sp =  $15\text{m}\Omega-\text{cm}^2$ ," *Electron. Lett.*, vol. 39, no. 1, pp. 152–154, Jan. 2003.

- [10] H. F. Hamann, A. Weger, J. A. Lacey, Z. Hu, P. Bose, E. Cohen, and J. Wakil, "Hotspot-limited microprocessors: Direct temperature and power distribution measurements," *IEEE J. Solid-State Circuits*, vol. 42, no. 1, pp. 56–65, Jan. 2007.

- [11] S. M. Sze, *Physics of Semiconductor Devices*, 2nd ed. New York: Wiley, 1981, p. 447.

- [12] B. J. Baliga, Power Semiconductor Devices. Boston, MA: PWS-Kent, 1996, pp. 367–373.

Robert S. Howell (S'92–M'01) received the B.S. degree in engineering (with distinction) and the B.A. degree in history (with distinction) from Swarthmore College, Swarthmore, PA, in 1995, and the Ph.D. degree in electrical engineering from Lehigh University, Bethlehem, PA, in 2000, developing polysilicon thin-film transistors and associated display technologies, including the first polysilicon circuitry fabricated on flexible metal foils.

Since completing his studies, he has been with Northrop Grumman Corporation, Linthicum, MD,

within the Electronic Systems Sector, where he has worked on a variety of high-power and/or high-frequency device and system development projects. These include works on SiC SITs and the 10-kV SiC DMOSFET, as well as GaN HEMTs and a variety of novel 3-D silicon device structures. He is currently a Fellow Engineer with Northrop Grumman Corporation. He is a holder of two patents and has over 30 publications in various refereed journals and conference proceedings.

**Ty R. McNutt** (S'01–M'04) received the B.S. degree in physics (with distinction) from Hendrix College, Conway, AR, in 1998, and the M.S.E.E. and Ph.D. degrees in electrical engineering from the University of Arkansas, Fayetteville, in 2001 and 2004, respectively. His M.S.E.E. work focused on the development of thermal-based data isolation techniques in silicon-on-insulator CMOS for systems-on-a-chip applications.

He was a Guest Researcher with the National Institute of Standards and Technology from 2000 to

2004, concentrating on the characterization and modeling of silicon carbide power devices. In 2004, he was with the Compound Semiconductor Research Group, Advanced Materials and Semiconductor Device Technology Center, Northrop Grumman Corporation, Linthicum, MD. While at Northrop Grumman Corporation, he helped develop high-power SiC devices to provide drastic size and weight savings for naval- and land-combat-focused systems. Currently, he is a Program Manager with the Advanced Concepts and Technologies Division, Northrop Grumman Corporation. He has coauthored over 40 publications in various refereed journals and conference proceedings, and he is an Associate Editor of the *International Journal of Power Management Electronics*.

**Steven Buchoff** attended the University of Maryland, College Park and the University of Maryland, Baltimore County with a major in biochemistry from 1972–1974.

He was with Westinghouse (currently Northrop Grumman Corporation's Electronic Systems Sector), Linthicum, MD, in 1981 as a Solid State Technician, where he worked in PVD silicon processing for 16 years. Moving from semiconductor fabrication to failure analysis, he was with the Failure Analysis Group, with chief responsibility for the FESEM, as

well as other FA tools and processes. Most recently, he has been working on SiC device process development, having spent 6 years working on the development of advanced SiC power devices, such as the implanted SiC SIT device and the 10-kV SiC DMOSFET. He is currently working on maintaining and developing new photolithographic processes for Si and SiC microelectronic fabrication.

**Andris Ezis** (M'88–SM'08) received the B.Sc. degree in physics and electronic engineering and the Ph.D. degree in electronic engineering from the University of Leeds, Leeds, U.K., in 1977 and 1981, respectively.

From 1982 to 1994, he was with Universal Energy Systems, Inc., Dayton, OH. From 1982 to 1984, he was a Visiting Scientist with Wright Patterson AFB, Dayton, OH, where he conducted research on transient annealing of ion-implanted GaAs. From 1984 to 1990, he was the Principal Investigator

of programs with Wright Patterson AFB where he carried out research on AlGaAs/GaAs MODFETs and AlGaAs/GaAs narrow-base HBTs. From 1991 to 1994, he was the Principal Investigator and the Program Manager of phase II SBIR programs on the monolithic integration of DBR lasers and the fabrication of bonded SOI. Since 1994, he has been with Northrop Grumman Corporation, Linthicum, MD, where he is currently a Senior Advisory Engineer. He is responsible for the HBT foundry process, which he transitioned from AlGaAs/GaAs to InGaP/GaAs. His present work is focused on enhancing the HBT technology and increasing the level of integration. His work has also extended to SiC diode, JFET, GTO, and MOSFET devices for high-power applications.

**Stephen Van Campen** (M'99) received the B.S. degree in physics with a concentration in electrical engineering from Clarkson University, Potsdam, NY, in 1987, and the M.S. and Ph.D. degrees in physics from Lehigh University, Bethlehem, PA, in 1989 and 1994, respectively.

His graduate research was in quantum mechanical semiconductor devices, and he was able to build and measure properties of 2-D quantum systems in silicon MOSFETs. He was then with Kimball Physics Inc., Wilton, NH, until 2000,

where he characterized custom electron and ion sources. There he developed field emission and thermionic cathodes, troubleshot high-voltage electron guns, and developed fabrication techniques for cathode and electron guns. Since 2000, he has been with Northrop Grumman Corporation, Linthicum, MD, where he has been the Principle Investigator of several silicon carbide power switch programs which developed high-power semiconductor devices such as the 10-kV SiC MOSFET, JBS diodes, p-indiodes, 7-kV GTO thyristors, and an all-SiC cascode switch designed at 1200 V for commercial applications. He continues doing research in a variety of semiconductor technologies and is currently the Manager of the Advance Technology Development at Northrop Grumman Corporation's ATL facility.

Bettina Nechay (S'94–M'06) received the B.S. degree in physics (with distinction) and in electrical engineering from Rensselaer Polytechnic Institute, Troy, NY, in 1987 and 1988, respectively, and the M.S. and Ph.D. degrees in applied physics from Stanford University, Stanford, CA, in 1992 and 1996, respectively. Her Ph.D. work focused on the development of an ultrafast noncontact electrical force microscope for probing voltages in circuits and devices with ∼1-ps time resolution and nanometer-scale spatial resolution.

She was a Postdoctoral Researcher with the Swiss Federal Institute of Technology (ETH), Zurich, Switzerland, from 1996 to 1999, developing a pump-probe spectroscopic measurement system using an NSOM, and using this system to measure local carrier dynamics in various semiconductor structures. After her postdoctoral work, she was with Lucent Technology in 1999 (later spun off as Agere Systems), concentrating on the design and measurement of electroabsorption-modulated lasers for fiber-optic telecommunications, as well as on the fiber-optic communication system characterizations of distributed feedback lasers, electroabsorption-modulated lasers, and avalanche photodiodes. Since 2005, she has been with the Compound Semiconductor Research Group, Advanced Materials and Semiconductor Device Technology Center, Northrop Grumman Corporation, Linthicum, MD. While at Northrop Grumman Corporation, she helped design, fabricate, and characterize high-power SiC devices. She has coauthored over 20 publications in various refereed journals and conference proceedings.

**Christopher F. Kirby** (M'08) received the B.S. and Ph.D. degrees in chemical engineering from The Johns Hopkins University, Baltimore, MD, in 1993 and 2000, respectively. His Ph.D. work was on polymer physics inside of supercritical fluids.

Since graduation, he has been with Electronic Systems Sector, Northrop Grumman Corporation, Linthicum, MD, where he leads the process development for several MEMS device efforts. He has continued working in process development and integration, including SiC for high-power high-

frequency applications, and in 3-D integration and other novel 3-D device and circuit fabrication techniques. He is a holder of one patent and has published over 15 papers in journals and conferences.

**R.** Chris Clarke (M'91–SM'93–F'06) received Higher National Certificates in chemistry and electrical engineering from Worcester University, Worcester, U.K.

He is currently a Program Director with Northrop Grumman Corporation, Linthicum, MD, where he is responsible for the direction and development of new technology for advanced systems. He is an accomplished and respected Leader in the fields of new materials growth, new device development, and transfer of technology to production. He performed

the original work on vapor-phase epitaxy of pure and doped GaAs and InP films for microwave devices, both for millimeter-wave Gunn diodes and X-band MESFETs. Original investigative material work was also performed on the activation of ion-implanted impurities in gallium arsenide and on the impact of subsurface damage on devices fabricated in undoped GaAs substrates. More recently, CVD growth of 6H- and 4H-SiC was pioneered for the pure and doped structures required in the fabrication of the first 4H-SiC MESFET and SIT microwave devices. Recent research areas include GaN-AlGaN CVD, SiC hot-wall CVD, and aluminum nitride bulk crystal growth for microwave applications. Expert in the design of high-voltage microwave transistors, he has authored papers on high-efficiency castellated FETs and high-voltage GaAs power MESFETs. His UHF SiC SITs currently hold the record for the highest reported microwave power and efficiency of any semiconductor material, providing a sixfold improvement in power output per package when compared with commercial GaAs and silicon products.

Marc E. Sherwin (M'92) received the B.S. degree in electrical engineering and the B.A. degree in physics from Rensselaer Polytechnic Institute, Troy, NY, in 1987, and the M.S. and Ph.D. degrees in electrical engineering from the University of Michigan, Ann Arbor, in 1992. His thesis work focused on InP epitaxy by chemical beam epitaxy.

His postgraduate work was performed at Sandia National Laboratories where he was involved in GaAs JFET simulation and fabrication, as well as device fabrication for single electronic quantum de-

vices. He was then with M/A-COM as both Process Engineer and Engineering Manager involved in GaAs MMIC fabrication. He then worked for Emcore as a Fab Manager for the GaAs VCSEL and triple-junction solar-cell production lines. Since 2004, he has been with the Electronic Systems Sector, Northrop Grumman Corporation, Linthicum, MD, and is currently the Deputy Director overseeing microsystems research and development in such diverse areas as power electronics, RF devices, and nanotechnology. Over the years, he has coauthored many articles and numerous conference presentations, including such topics as InP epitaxy, theoretical stress and device calculations, e-beam lithography, and shop-floor control software.

Ranbir Singh (M'03) received the B.Tech. degree in electrical engineering from the Indian Institute of Technology, New Delhi, India, in 1990, and the M.S. and Ph.D. degrees in electrical engineering from North Carolina State University, Raleigh.

He conducted extensive research on a wide range of SiC power devices including MOSFETs, IGBTs, field-controlled thyristors, and JBS, p-i-n, and Schottky diodes at Cree, Inc., Durham, NC, from 1995 to 2003. Then, he was a Visiting Researcher at the National Institute of Standards and Technol-

ogy, Gaithersburg, MD. Thereafter, he founded GeneSiC Semiconductor, Inc., Dulles, VA, a company that focuses on exploiting the superior properties of silicon carbide and other wide-bandgap semiconductors toward high-power, high-temperature, ultrahigh-voltage, and particle/photonic detectors. He is a holder of 21 issued U.S. patents and has coauthored over 90 publications in various refereed journals and conference proceedings. He is the author of the book entitled "Cryogenic operation of silicon power devices" (Kluwer, 1998). He has made two invited MRS presentations.

Dr. Singh served on the Technical Committee of the International Symposium on Power Semiconductor Devices and ICs from 2002–2004 and was part of a panel to develop a roadmap for the insertion of SiC-based power devices into commercial applications. In 2003, and then again in 2004, he received the IEEJ Technical Development Award for the development of ultrahigh-voltage SiC devices.